Menuju Akhir

TUGAS PENDAHULUAN

PERCOBAAN 2 KONDISI 4

1. Kondisi (Daftar Isi)

Buatlah rangkaian seperti pada modul percobaan, kemudian buatlah kondisi dengan inputan berupa saklar SPDT.

· Rangkaian Sederhana 1 : B= 1, D=1, A=0, C’=1, D= 1

· Rangkaian Sederhana 2 : B= 1, D=1, A= 1, B=1, C’=0

2. Gambar Rangkaian Rangkaian (Daftar Isi)

3. Video Simulasi (Daftar Isi)

4. Prinsip Kerja Rangkaian (Daftar Isi)

Pada rangkaian diatas terdapat 2 rangkaian sederhana yang mana rangkaian 1 dengan kondisi B = 1, D=1, A=1, C'=0, D=1, sedangkan rangkaian 2 dengan kondisi B=1,D=1,A=1,B=1,C'=0. maka pada pembahasan akan dibagi sesuai dengan rangkaian masing-masing.

Rangkaian 1

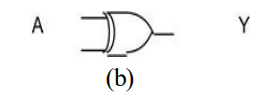

Pada rangkaian ini, digunakan 5 saklar SPDT sebagai input yang terhubung dari sumber ke gerbang logika dan ground yang mana digunakan 3 gerbang logika yaitu AND dan X-OR dimana gerbang AND bekerja dengan mengalikan seluruh masukan sehingga menghasilkan 0 dengan proses dimana pada A, C' dan D dengan proses (0*1*1) menghasilkan 0 dan gerbang X-OR akan berlogika 0 sesuai prinsip dari gerbang X-OR dimana pada prosesnya melalui hasil dari B dan D (1+1) itu menghasilkan 2 dan 2 merupakan angka genap maka akan menjadi 0. lalu masuk ke gerbang OR menjadi 0 + 0 = 0. sehingga keluaran dari rangkaian 1 adalah 0.

Rangkaian 2

Pada rangkaian ini, digunakan 5 saklar SPDT sebagai input yang terhubung dari sumber ke gerbang logika dan ground yang mana digunakan 3 gerbang logika yaitu AND dan X-OR dimana gerbang AND bekerja dengan mengalikan seluruh masukan sehingga menghasilkan 0 dengan proses dimana pada A, C' dan D dengan proses (1*1*0) menghasilkan 0 dan gerbang X-OR akan berlogika 0 sesuai prinsip dari gerbang X-OR dimana pada prosesnya melalui hasil dari B dan D (1+1) itu menghasilkan 2 dan 2 merupakan angka genap maka akan menjadi 0. lalu masuk ke gerbang OR menjadi 0 + 0 = 0. sehingga keluaran dari rangkaian 1 adalah 0.

5. Link Download (Daftar Isi)

Download HTML

Download Rangkaian Percobaan

Download Video Simulasi Percobaan

Menuju Awal

.png)

.png)

.png)