PERCOBAAN 2

1. Jurnal (DAFTAR ISI)

2. Alat dan Bahan (DAFTAR ISI)

a. Module D’Lorenzo

b. Jumper

c. Decoder 74LS47

d. Seven Segment Common Anoda

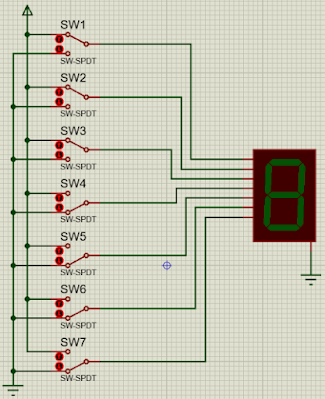

3. Rangkaian Simulasi (DAFTAR ISI)

4. Video Rangkaian (DAFTAR ISI)

5. Analisa (DAFTAR ISI)

1. Analisa pengaruh LT, RBO, RBI, jika diaktifkan

- Lamp Test (LT)

LT memiliki fungsi mengatur LED pada sevent segment. Ketika LT aktif maka akan membuat LED pada sevent segment dapat menyala.

-

Ripple-Blanking

Output (RBO)

Jika pada seven segment ingin menampilkan

0-15 maka RBO harus high (berlogika 1). Namun ketika RBO low (berlogika 0)

semua segmen output akan berlogika high terlepas dari keadaan kondisi input

lainnya (lampu pada segmen mati).

-

Ripple-Blanking

Input (RBI)

Ketika RBI dan input A, B, C, dan D berada pada logika

0 (low), LT high dan output RBO akan low dan semua segmen output menjadi berlogika

high.

2. Analisa pengaruh bcd decoder to seven segment pada

rangkaian

BCD decoder akan memudahkan mengubah output biner ke

decimal yang ditampilkan pada seven segment. Pada BCD decoder input sebanyak 4

biner akan diubah menjadi sebanyak tujuh output.

.png)

.png)

.png)

.png)